But that cannot be right because Zo will change according to the 2X_Q output clock frequency!

Why would Z0 change by frequency? It's the characteristic impedance of the trace.

But that cannot be right because Zo will change according to the 2X_Q output clock frequency!

But let's ignore that for now and assume a fixed Zo impedance that never changes. How do we explain what Apple wrote on the schematic with regard to Rp values?

Why would Z0 change by frequency? It's the characteristic impedance of the trace.

As the frequecy varies, so to do impedance of the capacitance and the inductance.

Right, that makes sense. For practical purposes though, doesn't the impedance virtually flatten above 1MHz?

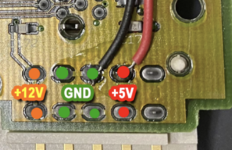

You can see that in my photo here...Sometimes they run GND traces on either side of CLK traces, to remove the unknown.

But again, I would like to say that I am not touching resistor Rp at all. It is still 140Ω, which according to Apple's schematic is the right choice only for a 33MHz clock speed selection. For 40MHz, Rp should be 110Ω. And above 40MHz, it becomes a guessing game, as we discussed earlier today.

Measuring is difficult to impossible without soldering long wires to the points to be measured, due to the fact the motherboard must be inserted into the Color Classic in order to be powered. Also, the high frequency signals we are talking about are twice the base CPU clock speed, so 80MHz for a 40MHz base clock.Measuring the peak to peak voltage with a scope (at the destination) can help you tune that value.

But your waveforms look pretty good. I don't see a bunch of ringing even with the larger Rp still installed.

No, unfortunately I do not. But I do have a genuine spinning platter hard drive installed internally in my Mystic, and I can power or kill power to it by yanking out or connecting it's power plug.Do you have a SCSI2SD v6?

SUMMARY: With MacSD or BlueSCSIv2, my Mystic boots fine into all OSs from 7.1 thru 8.1 at 43.2MHz, but only boots into 7.1 and 7.5.5 at 48MHz. It freezes at the Welcome to Macintosh splash screen on 7.6.1 and 8.1. But again, my spinning platter HDD doesn't freeze.

This isn't a complaint, mind you. I am just genuinely curious what could be happening on a hardware level that would allow my spinning HDD to work fine with System 7.6.1 and OS 8.1 at higher CPU clock speeds whereas MacSD and BSv2 do not. It's research.

I cannot answer that question until I test again, which won't be until late tonight after work. Thursdays are my late nights when I don't get home until past 10pm.What is the state of the MacSD LEDs when it freezes?

Yes. As discussed in my earlier post, SCSI_Clk attaches to CK on the 53C96 SCSI controller chip, and SCSI_Clk is feed by Q_DIV_2. So for example, if the CPU is clocked at 48MHz, Q would be 48MHz, and that divided by 2 is 24MHz going into SCSI_Clk, which in turn is 24MHz going into CK of the 53C96 SCSI controller chip.Is the clock to the SCSI chip affected by your overclocking?