I swapped my SE/30's FPU for a 40MHz part, then fed it a 31.33MHz clock, tapped from the glue chip.

The first step was removing the 16MHz FPU:

Pin 11 on the FPU is the clock input. I bent it outward so it doesn't contact the pad:

Pin 11 on the FPU is connected to the 31.33MHz clock at pin 17 of the glue chip. The wire passes through a via next to pin 17:

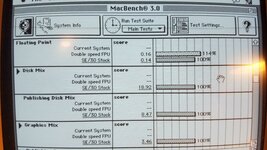

Results from MacBench 3.0 and Speedometer 4.0.2:

A bit underwhelming considering clock speed is doubled, but it's an improvement. A 40 MHz oscillator would push it further and still be within spec.

MacBench floating point: +14%

Speedometer FFT: +11%

Speedometer KWhet: +16%

Speedometer matrix: +20%

Speedometer average: +25%

The first step was removing the 16MHz FPU:

Pin 11 on the FPU is the clock input. I bent it outward so it doesn't contact the pad:

Pin 11 on the FPU is connected to the 31.33MHz clock at pin 17 of the glue chip. The wire passes through a via next to pin 17:

Results from MacBench 3.0 and Speedometer 4.0.2:

A bit underwhelming considering clock speed is doubled, but it's an improvement. A 40 MHz oscillator would push it further and still be within spec.

MacBench floating point: +14%

Speedometer FFT: +11%

Speedometer KWhet: +16%

Speedometer matrix: +20%

Speedometer average: +25%

Last edited: