Problem with that is that you'd need to solder a castellated PCB in place as the pads are SMD. That's a bit fiddly to say the least.Definitely, sick indeed!

I've been looking at doing similar things with Macs hobbled by undersized banks of onboard RAM for years. I wonder if the approach I've been pursuing would work for you?

Instead of stacking Chips, remove them and build a "VRAM SIMM Expander" for the single VRAM slot that will service two SIMMs. One is addressed as usual, the second would be on the shared bus, but jumpered to CAS/RAS on the vacated pads of the stock VRAM ICs with the balance jumpered to the unimplemented lines on the controller as you have done.

Pet projects of mine are IIsi, Q605 and Q630. IIsi is a 30pin PITA, but I've had that one worked out for the longest. Haven't been able to find my Q630 board so I can't use the 72pin SIMM expanders I have on hand.

Q605 is too low in profile to use same expanders I have on hand.So I need to finalize my notion for a "reverse slope" low profile 72pin SIMM expander. Same deal, desolder the DRAM ICs of Bank A and jumper their CAS/RAS lines to expander slot two and jumper the remainder to the memory controller's unimplemented lines.

Such was done somewhere out on the web to a Q605 in the early days of 'fritter to achieve max controller supported RAM loadout. It worked, but was a horrible thing to behold and a kluge so nasty that dr. bob dubbed it the "Evil RAS Line Hack."

Is this making any sense to you? I'm tired.

IOW: instead of doing the agonizing, amazing, beautiful job of IC stacking that Garret has done in your 660AV, you'd just desolder the friggin' things. Then install the new contraption in the VRAM SIMM Slot and whale away with soldering iron connecting jumper wires from ready made locations on the expander to requisite pads on the board and legs of the controller.

The pair of VRAM SIMMs can be removed, but the expander with its two slots servicing all four banks remains forever in place.

Mod: Quadra 660AV 2 MB VRAM Upgrade

- Thread starter Zane Kaminski

- Start date

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Not sure what you mean by that?

PCB is in the one existing slot with both SIMMs on board. Pads are vacated and only the CAS/RAS control line bodge wires are soldered to them.

IIsi is a PITA as the data bus is disjointed on the controller. Otherwise I'd be using adapters in the existing SIMM slots with both banks implemented on 72pin SIMMs. Data lines need to be jumpered to the adapter board as well as control lines on my favorite little fetal pig. I'll have to dig up my thread(s) about it and update. I've got double row RA header assemblies to epoxy(?) on top of the still soldered DRAM ICs of the IIsi. Chip select legs are lifted for A/B switch select on adapter for testing with onboard DRAM or the 72 pin SIMMs

Didn't check, WAG here is that data bus is unified in VRAM applications, more like SRAM operationally?

Solderd DRAM Bank obliteration should probably be in its own thread, mentioned it in passing as the rest of us aren't up to meticulous chip stacking. I once was, but have aged out of patience required for it and not ready to prove beyond doubt that hands no longer qualify for rock steady classification.

PCB is in the one existing slot with both SIMMs on board. Pads are vacated and only the CAS/RAS control line bodge wires are soldered to them.

IIsi is a PITA as the data bus is disjointed on the controller. Otherwise I'd be using adapters in the existing SIMM slots with both banks implemented on 72pin SIMMs. Data lines need to be jumpered to the adapter board as well as control lines on my favorite little fetal pig. I'll have to dig up my thread(s) about it and update. I've got double row RA header assemblies to epoxy(?) on top of the still soldered DRAM ICs of the IIsi. Chip select legs are lifted for A/B switch select on adapter for testing with onboard DRAM or the 72 pin SIMMs

Didn't check, WAG here is that data bus is unified in VRAM applications, more like SRAM operationally?

Solderd DRAM Bank obliteration should probably be in its own thread, mentioned it in passing as the rest of us aren't up to meticulous chip stacking. I once was, but have aged out of patience required for it and not ready to prove beyond doubt that hands no longer qualify for rock steady classification.

Last edited:

There's a documented method for reliable QFP conversion to BGA from back in the day out there, but not posting about it in open forums.Problem with that is that you'd need to solder a castellated PCB in place as the pads are SMD. That's a bit fiddly to say the least.

Been ruminating on this one whilst doing other things. It struck me that the VRAM SIMM expander only needs to support a 256K SIMM alongside the 512K SIMM as the 256K Bank on board will remain to complete the loadout. That would simplify things quite a bit in terms of bodge line requirements I think?

Doesn't work that way at all for DRAM Bank obliteration/SIMM replacement hijinks.

Doesn't work that way at all for DRAM Bank obliteration/SIMM replacement hijinks.

Instead of stacking Chips, remove them and build a "VRAM SIMM Expander" for the single VRAM slot that will service two SIMMs. One is addressed as usual, the second would be on the shared bus, but jumpered to CAS/RAS on the vacated pads of the stock VRAM ICs with the balance jumpered to the unimplemented lines on the controller as you have done.

Pet projects of mine are IIsi, Q605 and Q630. IIsi is a 30pin PITA, but I've had that one worked out for the longest. Haven't been able to find my Q630 board so I can't use the 72pin SIMM expanders I have on hand.

Q605 is too low in profile to use same expanders I have on hand.So I need to finalize my notion for a "reverse slope" low profile 72pin SIMM expander. Same deal, desolder the DRAM ICs of Bank A and jumper their CAS/RAS lines to expander slot two and jumper the remainder to the memory controller's unimplemented lines.

Such was done somewhere out on the web to a Q605 in the early days of 'fritter to achieve max controller supported RAM loadout. It worked, but was a horrible thing to behold and a kluge so nasty that dr. bob dubbed it the "Evil RAS Line Hack."

Is this making any sense to you? I'm tired.

IOW: instead of doing the agonizing, amazing, beautiful job of IC stacking that Garret has done in your 660AV, you'd just desolder the friggin' things. Then install the new contraption in the VRAM SIMM Slot and whale away with soldering iron connecting jumper wires from ready made locations on the expander to requisite pads on the board and legs of the controller.

The pair of VRAM SIMMs can be removed, but the expander with its two slots servicing all four banks remains forever in place.

mmmhhh there is NO VRAM slot on the 660AV in fact, all soldered to the motherboard.

Indeed, thanks for that correction. I was likely conflating two different approaches to DRAM expansion in a half awake state. On board SIMM in the Q605 was confuddled with the IIsi soldered DRAM examples got confuzzled.

To further explain/confuse things:

1 - As Kai noted, the onboard VRAM would be desoldered and replaced by a castellated adapter PCB.

- - - In the 660AV two would be required, one on one side and other side of the dang chips in the way

2 - Adapters would convert the VRAM Chip's Pads to VRAM slots, but that's not well thought through

3 - Soldering the desoldered mobo chips and desoldered chips from desoldered SIMM chip to adapter would be better

Questions:

1 - Are the 660AV and 840AV the only 68K Macs with all VRAM soldered to the mobo?

2 - Thinking here is that the bus speed of the 840AV made timings for VRAM SIMMs problematic?

3 - 840AV soldered VRAM layout carried over to 660AV on its slower bus?

Thinking fiddly chip stacking would be the way to go rather than fiddly castellated board installation. If timing constraints are at issue for the shared AV controller the chip stacking approach is the only way to go. It's also a tried and true KISS principle correct methodology.

< swerves back on topic from tangent >

@Zane Kaminski how goes your stacking experiment? Haven't heard form you in a while. Has the mod been stable?

@iPhil64 thanks for resurrecting this project!

To further explain/confuse things:

1 - As Kai noted, the onboard VRAM would be desoldered and replaced by a castellated adapter PCB.

- - - In the 660AV two would be required, one on one side and other side of the dang chips in the way

2 - Adapters would convert the VRAM Chip's Pads to VRAM slots, but that's not well thought through

3 - Soldering the desoldered mobo chips and desoldered chips from desoldered SIMM chip to adapter would be better

Questions:

1 - Are the 660AV and 840AV the only 68K Macs with all VRAM soldered to the mobo?

2 - Thinking here is that the bus speed of the 840AV made timings for VRAM SIMMs problematic?

3 - 840AV soldered VRAM layout carried over to 660AV on its slower bus?

Thinking fiddly chip stacking would be the way to go rather than fiddly castellated board installation. If timing constraints are at issue for the shared AV controller the chip stacking approach is the only way to go. It's also a tried and true KISS principle correct methodology.

< swerves back on topic from tangent >

@Zane Kaminski how goes your stacking experiment? Haven't heard form you in a while. Has the mod been stable?

@iPhil64 thanks for resurrecting this project!

Hehe ! @Zane Kaminski Sorry for coming back a bit late, I had many other projects, including building 2 x SE reloaded boards and repairing a few machines.

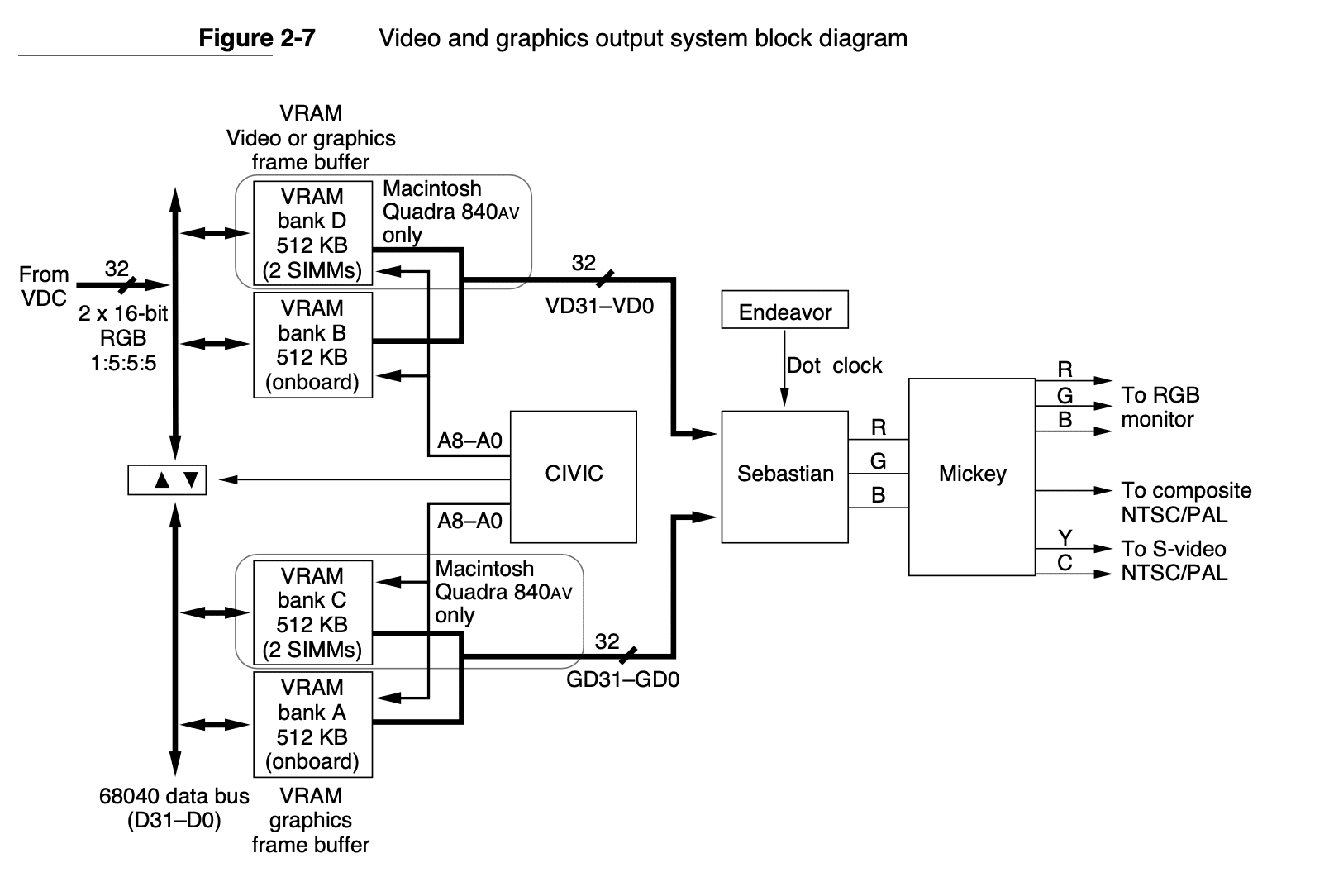

In fact, only half of the memory is soldered on the 840AV, which has two VRAM expansion slots.

From Apple documentation, you can see bank C and D are on SIMMs, whereas a and B are soldered on both models.

(yes, there was a time Apple did provide documentation).

In fact, only half of the memory is soldered on the 840AV, which has two VRAM expansion slots.

From Apple documentation, you can see bank C and D are on SIMMs, whereas a and B are soldered on both models.

(yes, there was a time Apple did provide documentation).

Yes! So on the 840AV when you install VRAM SIMMs in the slots, you are doing the same thing electrically as I did with the mod. I was inspired to do the mod after reading the Developer Note and the video init code which is run at startup. The video init routine measures the RAM size rather than by checking if it's a 660AV or 840AV so I figured the mod would work without and software mods.Hehe ! @Zane Kaminski Sorry for coming back a bit late, I had many other projects, including building 2 x SE reloaded boards and repairing a few machines.

In fact, only half of the memory is soldered on the 840AV, which has two VRAM expansion slots.

From Apple documentation, you can see bank C and D are on SIMMs, whereas a and B are soldered on both models.

(yes, there was a time Apple did provide documentation).

But unfortunately the only practical way to do the mod I'm aware of is with chip stacking and modwires. We have discussed a lot of interesting ideas, e.g. a "mezzanine board" with pins on the bottom soldered to the onboard VRAM array pads and which provides several VRAM slots. But that's even more difficult to solder than the stacked VRAM chips. Due to its large size, the mezzanine board will not have adequate coplanarity on the bottom pins. Some pins will be a little taller or shorter, there will be error in the pin angles, etc. So after reflowing the mezzanine board onto the VRAM array pads, you'll likely end up with unsoldered pins, and some of them will be in the middle of the mezzanine board where it will be very difficult to fix them with hand soldering. The VRAM chips are sort of difficult to stack but they are smaller and you can fix shorts/opens between the pins/board more easily than you can attach some big gizmo on top of the former RAM array.

Has been working stably since March@Zane Kaminski how goes your stacking experiment? Haven't heard form you in a while. Has the mod been stable?

So after reflowing the mezzanine board onto the VRAM array pads, you'll likely end up with unsoldered pins, and some of them will be in the middle of the mezzanine board where it will be very difficult to fix them with hand soldering.

Perhaps put plated vias in the pads, so if they fail to make connection, you can solder down the hole? It reduces your pad to pad area but provides a more reliable method of insuring solder contact.

There's a process I don't talk about on public forums to be used if I ever get around to doing an interstitial layer G3 adaptation for my 2300c that seems far better than castellation. It involves little spherical doodads pressed onto the adapter board in rows above each pad. It could be an intellectual property quagmire in the making of it.

Zane, It's good to have the 840AV Bomarc schematics for reference, do we know if the 660AV one do exist ? I'm looking specifically for things around the clock generation for the Spicy O'clock thread... I guess they are similar, just checking.I’ve attached some pictures from the 840AV Bomarc schematic showing the wiring for the “X” and “Y” VRAM banks. I should be able to duplicate this on the 660AV with piggybacked chips and only four bodge wires.

But will the ROM / Mac OS recognize the extra VRAM?

I have not seen any for the 660AV so I don’t think they have been published. However the 840 and 660 are based on the same exact chipset and architecture so I’ve had success just looking at the 840 schematic and ignoring the stuff that I know isn’t on the 660Zane, It's good to have the 840AV Bomarc schematics for reference, do we know if the 660AV one do exist ? I'm looking specifically for things around the clock generation for the Spicy O'clock thread... I guess they are similar, just checking.

Last edited:

Yes, they are definitely close, and the Apple developer notes helps as well.I have not seen any for the 660AV so I don’t think they have been published. However the 840 and 660 are based on the same exact chipset and architecture so I’ve had success just looking at the 840 schematic and ignoring the stuff that I know isn’t on the 660

I was just looking for clarifications around the clock divider as you may have seen in the Spicy O'Clock thread.

A few differences on the clock generation topic. Nothing major, but I'm unsure if it affects my ('unsuccessful) results.