Done playing with form factors, time to get on with the technical hurdles:

First approximation:

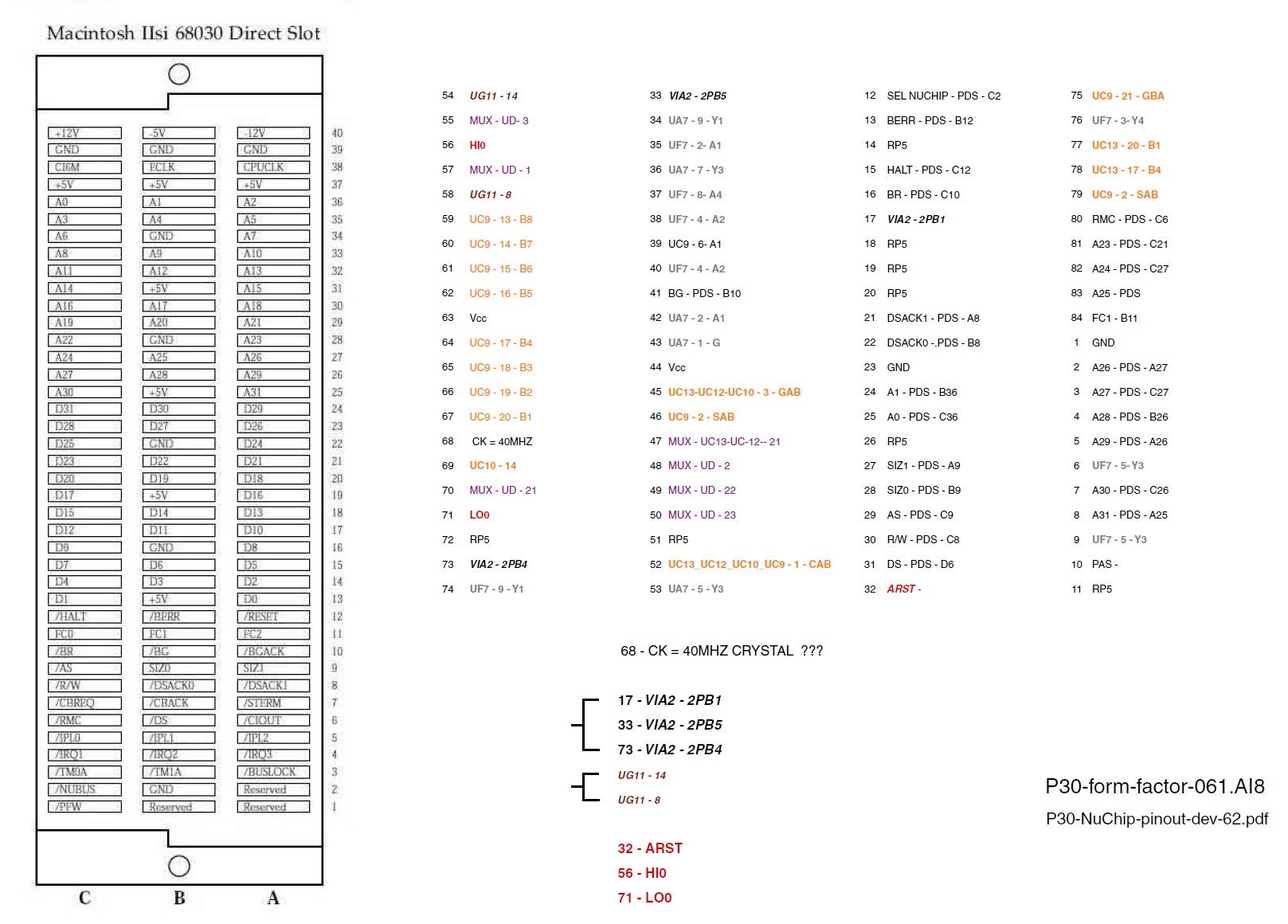

I was hoping that patching the three VIA2 signals to the three reserved pins on the SE/30 PDS would be sufficient.

Out of curiosity, are those pins grounded. Can't find my continuity tester ATM.

No such luck:

In the lower right corner of the IIcx NuBus Schematic Subsection there are two connections to UG11 on the IIcx which I haven't been able to locate on my @Bolle reworked SE/30 reloaded board.

Am I missing something?

And WTHeck are those three red pins? ARST, HI0 , LO0 .PDF attached for markup.

Little help here gang?

First approximation:

I was hoping that patching the three VIA2 signals to the three reserved pins on the SE/30 PDS would be sufficient.

Out of curiosity, are those pins grounded. Can't find my continuity tester ATM.

No such luck:

In the lower right corner of the IIcx NuBus Schematic Subsection there are two connections to UG11 on the IIcx which I haven't been able to locate on my @Bolle reworked SE/30 reloaded board.

Am I missing something?

And WTHeck are those three red pins? ARST, HI0 , LO0 .PDF attached for markup.

Little help here gang?

Attachments

Last edited: