What ROM does it use? Does it have Open Firmware?

ClassicHasClass answered that better than I could have. Yes, it has OF.

The S900 uses the same ROM as the Power Mac 7200&7500&8500&9500 v2 which doesn't have issues with PCI-PCI bridges. There's an S900 discussion at

https://68kmla.org/bb/index.php?thr...irmware-with-the-great-gazelle-pci-hack.45493 but it didn't get anywhere. Unless there is a problem visible in Open Firmware, then I can't fix it.

That's a little disappointing, although at this point in time, a solution for the S900 is more of a white whale than a real need.

Still, it's very puzzling. Architecturally, the S900 is like a PM9500 with the second bandit omitted and a PCI-PCI Bridge installed in Slot C1.

It does have a second CPU slot, but there's no active circuitry there unless a secondary CPU card is installed. There is one obscure item in my notes. I think that pins 186 and 187 on Bandit control what address it services. If my notes are accurate then on a 7200 both 186 and 187 are tied to 5V (through R). On the PTP 186 =>5V, 187 => GND for Bandit 1 and both go to 5V on Bandit 2. But on the S900 I show pins 186/187 tied to Gnd.

Would that even work with the same ROM if Bandit 1 was at a different address? Anyway, it's that one weird thing that might be different about the S900... Or a complete red herring.

Do chains of bridges work in the PM 9500 et. al.? This is relevant, because the first level of bridging does work on the S900. There's the PPB on slot C1 and then single function cards in the four dependent slots function just fine. The problem occurs when a second level of bridging occurs, or appears* to occur. Putting cards with PPBs behind the Slot C1 PPB is where the problem happens, unless that PPB-card is the only card installed in the bottom four slots.

*I write "appears" because I suspect dual head video cards and 2 port ATA cards don't actually have a physical PCI-PCI Bridge on board, although I suppose that functionality could be in their main chip.

Right. Probably for the DBDMA stuff that all the macio devices use.

And the Hardware Developer Notes for the various PowerSurge (X500/X600) and Catalyst (7200) machines clearly show Grand Central as a PCI device.

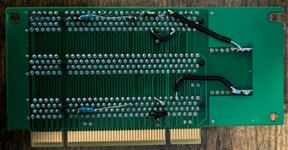

Those are the U13 and U15 in the 9500 schematics shown in the photos in this post:

https://68kmla.org/bb/index.php?thr...s-scans-of-a-powermac-9500-logic-board.39892/

U13 and U15 are wired differently in the 9500 schematics. Maybe they would have needed two different Bandit chips?

In my ancient tracings, U13 is connected to the G/R lines for Bandit 1, Grand Central, and Slots A1, B1, C1. U15 is connected to the G/R lines for Bandit 2, and slots D2, E2 and F2. Which makes sense. U13 arbitrates for the PCI bus created/bridged by U12/Bandit 1. U15 arbitrates for the PCI bus created/bridged by U14/Bandit 2.

Are they connected differently in some other way? Reversing Grant and Request lines or some such? That would be bizarre.

My notes also show Frame, IRDY, TRDY and RST connected to 343S0182.

Is there a picture with the 343S0018?

No, I don't have any pictures. I think I miswrote that note and it was probably a 343S1082. I did that signal tracing almost 20 years ago, so memory is very little help...

The MacIO chips (GrandCentral, OHare, Heathrow, Paddington) have multiple interrupt bits for different devices in MacIO and PCI. I suppose they all need to trigger the same CPU interrupt.

Yes, it appears that the CPUs have just one incoming interrupt signal and Grand Central and the others collect and perhaps manage in some way the interrupts. Internal register showing which interrupt(s) was triggered?