Got it, memory map must be addressing, testing and reporting reporting on it in a specialized bank? Maybe that's why it appears you've found five banks instead of four?I tried 0/8/16MB, 0MB gives death chimes anything else works but only 4MB is seen

Breaking the 36MB RAM limit on the LCIII

- Thread starter max1zzz

- Start date

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

@max1zzz forgot where I posted the new pic of the SIMMexpander with active components, but here are a couple from the iFrog collection. Still haven't found that dang project box. Found a this juicy bit of the docs in it though:

Four single or double sided 72pin SIMMs, I'll bet you're correct in your guess that the logic is decoding and generating additional RAS lines.

Four single or double sided 72pin SIMMs, I'll bet you're correct in your guess that the logic is decoding and generating additional RAS lines.

It would just be a single DIMM installed in the factory slot that needs a couple of wires soldered to the logic board.

I might of missed the answer to this while going through all the replies, but yeah, can't we just hook up the two lines to the existing 72-pin simm socket?

Been away/busy for several months. There is/was a 64MB composite SIMM by HP, 72 pin, that could be useful. It won't get you to 80, but would be a simple way to provide 64 + 4 and only modify the LCIII to the extent of running the RAS lines.

This HP SIMM has 4 banks of 16 on board but uses some logic to make them look like a single bank of 64.

So the SIMM would need modification to get the RAS lines right. Then it would plug directly into the LCIII SIMM slot. Connect the extra RAS lines and Bob's your uncle.

I'll try to better identify the SIMM later. It's about double height so I'm not sure about mechanics.

May be a while. I'm not really back.

These. Other auctions for same thing available first one I found. Should rcheck my facts. Working off old memories. Haven't examined them in ages.

HP A2580-80001 64MB ECC 60ns 72-Pin SIMM Memory Module for 9000 Workstation | eBay

Find many great new & used options and get the best deals for HP A2580-80001 64MB ECC 60ns 72-Pin SIMM Memory Module for 9000 Workstation at the best online prices at eBay! Free shipping for many products!www.ebay.com

If you guys want I could ask Chris at Memory Masters if he can make more 128MB 72-pin 5V FPM simms so you don't have to do all these crazy back flips to get a higher capacity 72-pin memory stick.

No idea.... I would need to dig through the LC475 devnotes and see how much free space is above the official RAM block in the memory map, IIRC the LCIII has just under 1GB free space above it's official RAM block so I would guess the 475 would be something similar, if that is the case one of those simm expanders could maybe get you as much as 512MB@max1zzz wondering about how much memory the Q605/475 might address using one of these puppies without jumpering Bank A to a better version? Got a guess? Can't get to anything to give it a whirl any time soon.

it's not just needing a higher capacity stick though, to get more than 36MB in the LCIII you need more banks. A 128MB stick will work just fine in a LCII but you will only get 32MB of usable memory form it as the LCIII lacks the needed address lines. the way this mod is working is by adding two extra banks of memory (AKA one extra SIMM slot as a 72pin simm can contain two banks)

I think what I am going to end up doing is creating a custom 4 bank SIMM for the LCIII, unfortunately my fancy simm riser did not work (I'm guessing the wires are just too long and create timing issues) and although I like the idea of creating a more universal solution I think getting something that can actually fit in a pizzabox case without creating timing issues is going to be more or less impossible

HRMMM? Doubtful that you'd have any timing issues at all cropping up? That's a unified 25MHz system bus, so only a ridiculous amount of latency from buffer or active components could be problematic? Traces could be a meter long on that clock I think. Maybe capacitance issues? Try isolating and then hardwiring VCC to your SIMM riser? I'll put a shiny nickel on power being the issue.

SIMMexpander was produced and used thru the NuBus PPC era on buses up to 33.6MHz as I understand it? Copyright date on mine is 1995, which puts it smack into that freq. on the system bus and 110MHz on the proc/memory bus from 1994's 8100/110 release, no?

SIMMexpander was produced and used thru the NuBus PPC era on buses up to 33.6MHz as I understand it? Copyright date on mine is 1995, which puts it smack into that freq. on the system bus and 110MHz on the proc/memory bus from 1994's 8100/110 release, no?

Last edited:

This might be a dumb question since my visualization of how 72-pin simm slots are wired is not very clear, but is there any way to modify the existing slot to make it so a 128MB simm would be recognized as 64MB? From what I understand 1 of the address lines is missing so that already cuts the potential capacity of a ram stick in half from 128MB to 64MB. What's preventing the existing socket from recognizing 64MB stick or half of a 128MB stick?

So I have enever been able to wrap my head around the maths, but my understanding i is that you need 11 address lines to fully address a 16MB bank (x2 banks on the simm for 32MB) and you need 12 to fully address 64MB (x2 banks on the simm for 64MB). I could be totally wrong though so if anyone with a better understanding of the maths wants to correct me please do!

Not maths I think? Seems a nomenclature kinda thing. You may be mixing computer numbers (binary) up with IRL decimals?

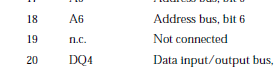

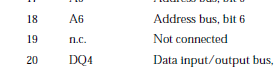

You need to have A11 implemented to address 64MB. That makes A0-A11, twelve address lines.

Diagram is from the everlasting SIMMspender hack aimed at torquing Bank A of the IIsi into supporting a full 64MB as in Bank A of the MDU based IIci.

The three bold lines are n.c. from MDU to Bank A on the logic board and so need bodge wiring. Dunno how this looks in schematics of your LCIII or my Q605/Q630 targets at present, but gut says it may be the same setup? IIsi schematic looks like Bank A may be wired up to support 8MB out of the box.

A0-A10 = addressing for 2MB

RAS0 + RAS2 = 4 Rows at 2MB each

= 2MB x 4 Rows = 8MB

edit: don't think that's the way Row Address Strobing works though. ISTR it being an EITHER/OR kinda thing? That would make 4MB supported in 2 Rows of traces to the buffered 1MB Vampire Video IIsi setup. While only 1MB is implemented, pads might support 4MB?

That's incredibly simplistic and fails to account for the function of Column Address Strobes. Haven't gotten that far yet, guessed I don't need to? Maybe @trag can find time to error check my notions and explain the function of CAS0-3. My Neanderthaler brain sees them as Strobing which bits are needed from the word accessed and where to look on the X axis of the memory Rows Strobed on the Y axis of the XY grid of memory? I've ignored that, methinks of the RAS/Address as supply lines in a plumbing diagram, don't need to visualize the branch lines for my purposes?

Gut tells me that there's confusion arising from the unfortunate use of the word Bank on SIMMs as opposed to memory Banks A and B on the machines I've looked into. In an MDU based system, CAS/RAS lines for Bank A and Bank B are discrete connections on that Memory Decoder Unit. I see the Banks of SIMMs on the Logic Boards as if they were two discrete fields on the farm that is the memory map in MDU Macs.

Here's my view of the problem on the IIsi which is I think, what you're facing in the LCIII?

Like I always try to explain, my brain doesn't grok schematic, boards are plumbing blueprints for electrons as above. I hope the diagram helps visual folks like myself? Sorry the color coding hasn't been fixed in this first revision, it's the only one I have available at present. RAS lines look like they may be wrong*** but may get the notion across?

*** ISTR breaking the unified light blue RAS line in the diagram into the two RAS lines implemented in later revisions. I've got a crazy complicated plumbing blueprint for turning the four 30pin SIMMs of Bank B into a single 72pin SIMM available in PDF, but won't post it unless you really wanna see it @max1zzz that sucker makes me crosseyed!

You need to have A11 implemented to address 64MB. That makes A0-A11, twelve address lines.

Diagram is from the everlasting SIMMspender hack aimed at torquing Bank A of the IIsi into supporting a full 64MB as in Bank A of the MDU based IIci.

The three bold lines are n.c. from MDU to Bank A on the logic board and so need bodge wiring. Dunno how this looks in schematics of your LCIII or my Q605/Q630 targets at present, but gut says it may be the same setup? IIsi schematic looks like Bank A may be wired up to support 8MB out of the box.

A0-A10 = addressing for 2MB

RAS0 + RAS2 = 4 Rows at 2MB each

= 2MB x 4 Rows = 8MB

edit: don't think that's the way Row Address Strobing works though. ISTR it being an EITHER/OR kinda thing? That would make 4MB supported in 2 Rows of traces to the buffered 1MB Vampire Video IIsi setup. While only 1MB is implemented, pads might support 4MB?

That's incredibly simplistic and fails to account for the function of Column Address Strobes. Haven't gotten that far yet, guessed I don't need to? Maybe @trag can find time to error check my notions and explain the function of CAS0-3. My Neanderthaler brain sees them as Strobing which bits are needed from the word accessed and where to look on the X axis of the memory Rows Strobed on the Y axis of the XY grid of memory? I've ignored that, methinks of the RAS/Address as supply lines in a plumbing diagram, don't need to visualize the branch lines for my purposes?

Gut tells me that there's confusion arising from the unfortunate use of the word Bank on SIMMs as opposed to memory Banks A and B on the machines I've looked into. In an MDU based system, CAS/RAS lines for Bank A and Bank B are discrete connections on that Memory Decoder Unit. I see the Banks of SIMMs on the Logic Boards as if they were two discrete fields on the farm that is the memory map in MDU Macs.

Here's my view of the problem on the IIsi which is I think, what you're facing in the LCIII?

Like I always try to explain, my brain doesn't grok schematic, boards are plumbing blueprints for electrons as above. I hope the diagram helps visual folks like myself? Sorry the color coding hasn't been fixed in this first revision, it's the only one I have available at present. RAS lines look like they may be wrong*** but may get the notion across?

*** ISTR breaking the unified light blue RAS line in the diagram into the two RAS lines implemented in later revisions. I've got a crazy complicated plumbing blueprint for turning the four 30pin SIMMs of Bank B into a single 72pin SIMM available in PDF, but won't post it unless you really wanna see it @max1zzz that sucker makes me crosseyed!

Last edited:

I don't really have time to sort out the whole diagram, but hopefully clarification/confirmation will be in the following details.That's incredibly simplistic and fails to account for the function of Column Address Strobes. Haven't gotten that far yet, guessed I don't need to? Maybe @trag can find time to error check my notions and explain the function of CAS0-3. My Neanderthaler brain sees them as Strobing which bits are needed from the word accessed and where to look on the X axis of the memory Rows Strobed on the Y axis of the XY grid of memory? I've ignored that, methinks of the RAS/Address as supply lines in a plumbing diagram, don't need to visualize the branch lines for my purposes?

First of all, on a 72-pin SIMM, 32 bits/4bytes are addressed at a time. So each address provides 32bit or 4 bytes of storage capacity.

Address lines are multiplexed which is a fancy way of saying they're used twice. The first part of the address is sent while the Row Address Strobe (RAS) is active and the second part of the address is sent on the same pins, but this time the Column Address Strobe (CAS) is active.

11 address lines gives 2 X 11 = 22 bits of address. 12 address lines gives 2 X 12 = 24 bits of address.

Some diagrams, unfortunately, label them A1 - A12 instead of A0 - A11, so exercise caution when reading documentation.

24 bits of address gives 2^24 => 16M of unique addresses.

Coming back to the special case of the 72-pin SIMM.

16M addresses, each of which addresses 4 bytes of storage gives 16M X 4bytes => 64 Megabytes of storage capacity. So each unique RAS line can address up to 64MB of storage, provided all 12 address lines are implemented.

In theory, the CAS lines should just correspond to the RAS lines, but from what I've seen regarding how SIMMs are wired, they are used to allow byte masking. "Masking" is a fancy term for taking/delivering only part of a dataword.

So if I have words that are 32 bits in length, and I only want bits 0 - 7, then I mask 8 - 31 so I don't read/write them.

I'm not sure whether the Mac ever uses this ability to of the memory to do partial reads/writes of the SIMMs.

In brief, if you have four RAS lines and four CAS lines, each RAS will go to all the chips in a single bank of memory. An example will be easier to understand, so let's assume we have four SIMM sockets and each socket has a single bank of RAM with it's own unique RAS line.

So RAS 0 => Bank/SIMM 0 (remember, in this case it's 1 bank per SIMM so they're the same)

RAS 1 => Bank/SIMM 1

RAS 2 => Bank/SIMM 2

RAS 3 => Bank/SIMM 3.

and one could do the CAS lines similarly if all you ever wanted to do was read the entirety of the chosen Bank/SIMM.

But what they do instead is:

CAS0 => 1st Byte in BANK/SIMM 0 - 3

CAS1 => 2nd Byte in BANK/SIMM 0 - 3

CAS2 => 3rd Byte in BANK/SIMM 0 - 3

CAS3 => 4th Byte in BANK/SIMM 0 - 3

Now, to read all of Bank 1, a 32 bit wide, 72-pin SIMM, you would use RAS 1, and all four of CAS0 - 3. But if you only want the fourth byte on Bank/SIMM 2, then you would use RAS 2 and only CAS 3.

============================================

The word Bank does get used in multiple ways unfortunately. When I use it regarding 72 - pin SIMMs it always means a group of memory chips sharing a single RAS connection. There are 4 unique RAS pins on the 72-pin SIMM specification. So, in theory, there could be up to four banks on single 72-pin SIMM. On Macs, in most cases, there are one or two unique RAS lines to each SIMM and those RAS lines drive four or two of the RAS pins (respectively) on the SIMM socket.

(Note: I haven't checked, but I'm pretty sure the Q605/LC/P475/476 has four unique RAS lines to its single SIMM socket because I was able to use a SIMM doubler to address two 128 MB SIMMs (64MB/Bank X 2 per SIMM => Four total 64 MB banks) in that machine.)

For DDR[n] memory, indivdual memory chips have multiple "Banks" and additional control lines for selecting them, so the term BANK gets even more messy.

I found a great webpage that I think answers all the questions I had regarding the wiring of 30-pin and 72-pin simms in a clear way:

https://www.retrotechnology.com/herbs_stuff/mac_banked_mem.txt

Part of the confusion I had was the from my loose definition of bank which I saw sometimes used interchangeably to refer to a memory stick. On top of that the correct term for what most people refer to a memory bank is actually supposed to be called memory rank now. I think this had a pretty thorough explanation:

https://www.digikey.ca/Site/Global/Layouts/DownloadPdf.ashx?pdfUrl=EE33DF78203D4692B71894E732852EA4

So for a 72-pin simm which is 32-bit, a rank would consist of a group of memory chips with the a total of 32 data lines.

Ok so now with all that clarified and with my current understanding are the following statements correct?

-Each memory rank is connected to a RAS line on the LC III memory controller.

-The LC III has 5 RAS lines.

-1 RAS line is connected to soldered memory rank on the logic board.

-2 RAS lines are connected to the existing memory socket (2 ranks).

-2 RAS lines are disconnected and could potentially be connected to another memory socket (2 ranks).

-Since there's only 11 address lines it's likely only 2K ram is supported by the memory controller of the LC III unless the 12th address line is also there but disconnected.

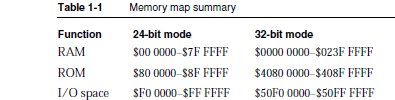

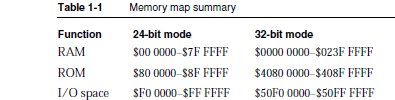

According to the developer doc for the LC III the memory map is defined for 36MB only. Seems to work for @max1zzz outside of that though.

The developer notes also shows A10 as not connected but that must be wrong or else you wouldn't be able to use 32MB simms.

I also found this interesting:

"At system startup, the boot code determines the amount of RAM installed in all banks and

then sets a RAM configuration register in Sonora."

Wonder what kind of configurations the Sonora chip supports. Couldn't find any dev notes on it though.

https://www.retrotechnology.com/herbs_stuff/mac_banked_mem.txt

The following information was copied from either Web page linked below.

It's an archive or the thread, on a forum, on macgurus.com:

MacGurus Technical Forums >

General Hardware and Software Discussions >

Memory and CPU Discussions >

subject: WTH is a "bank?"

The thread started in 2001. "trag" who is/was a "Guru Moderator", responded on date 12-08-2010, 12:15 PM, as follows.

----------------------------

Nine years late, but I probably didn't understand the material as well nine years ago...

Terms to consider, SIMM, DIMM, Single Sided, Double Sided, Banks or Banked.

The distinction between SIMM and DIMM is found on the memory module (SIMM or DIMM) connector -- the pins down along the bottom edge of the memory module.

A SIMM has a single row of pins. "But wait, I see pins on both side, isn't that double?" Yes, but electrically, it's one row of pins. Each pin is electrically connected to the pin opposite it on the flip side of the module. On most SIMMs, if you look closely, you'll see a tiny copper lined hole right at the top of each pin connecting it to the pin on the opposite side of the SIMM.

When you look into a SIMM socket, you'll see that the contacts for both sides of a module are made out of a single piece of wire bent to touch the pin on both sides of the board.

A DIMM has two rows of pins. The pins on each side of the module are electrically distinct. So, if the module is 84 pins long, it actually has 168 distinct pins, eight-four on each side.

Frankly, I'm not sure what the import of single and double sided is, other than to confuse people. I think folks try to use it as a short hand for banks. However, you can have a single banked module with chips on both sides or a double banked SIMM with chips only on one side depending on how the circuit board is laid out. As one might imagine, it's all about the electrical connections.

Okay, now on to the complicated stuff. To understand banks you'll need to understand something about how memory is addressed. In this case, I'll only be discussing FPM/EDO and possibly SDRAM (haven't looked at SDRAM specs.) DDR RAM does the same things as what I'm going to describe, but some of the details are so different as to make it a distinct topic.

The first thing to understand about memory is addressing. This is essential to understanding banks. I'm sorry, but there's no avoiding it. Addressing is how the computer keeps track of where it has put your data in the memory. The addresses are just numbers and they start at 0 and go up to some number which is related to the module's capacity.

On early 30 pin SIMMs there were 12 possible address lines or wires. Each address line can represent a 1 or a 0, they are an electrical representation of a binary number. So if we have twelve digits, and we're using base 2 (binary), how high can we count? 4096. Not very high. So how do you get a 16MB SIMM with only 12 address lines?

Simple, the computer sends a 12 bit (binary digits) address. Then the computer sends another 12 bit binary address. The memory gathers them up, strings them together and makes a 24 bit number out of them. This is called address multiplexing. A 24 bit number provides 2^24 or ~16M addresses.

30 pin SIMMs are one byte wide, so 16M addresses yields 16MB of capacity per SIMM.

What is width? When the computer gives the RAM an address, there is more than 1 bit of data stored at that address. How many bits? That's the data width. A 30 pin SIMM is 8 bits wide or one byte wide (eight bits to a byte). If your computer (such as the Mac II family) uses four 30 pin SIMMs at a time, then it is putting them together to get more width, in this case 4 X 8 = 32 bits of data width.

So a 30 bit SIMM has 12 address lines and is 8 bits wide. From this we deduce that the maximum capacity is 2^(12 X 2) X 8 = 16MB. The (12 X 2) is simply 12 address bits times 2 because of the multiplexing. Then we figure the total number of addresses from the number of address bits using the 2^. And X8 takes care of the eight bit width.

There's one more thing we need to know about 30 pin SIMMs before we can move on to the fun part. If you've been following closely, then a few paragraphs back you were probably asking yourself, "But how does the memory tell the difference between when it's getting the first 12 address bits and the last 12 address bits? Why doesn't it get them confused?"

That's the clever bit and the thing which ultimately will lead to banks.

The first 12 address bits are called the Row address. The second 12 address bits are called the Column address. When the computer is delivering the Row address it also activates the Row Address Strobe (RAS) wire. When the computer is delivering the Column address it activates the Column Address Strobe (CAS) wire. You may have seen RAS and CAS before when reading about refresh.

So, a memory module has RAS and CAS wires in addition to address wires (12 so far) and data wires (8 so far).

Now one more thing before we can move on to the joy that is banks. Memory module have the wires listed above, and so do memory chips, except that the memory chips don't have 8 data wires. An 8 bit wide memory chip would be very unusual (well not so unusual in modern DDR2 RAM). Back in the 30 pin SIMM days, each memory chip usually had one (1) data wire.

So, to make an eight bit wide SIMM, one installed eight 1 bit wide memory chips. The chips all shared the address and RAS and CAS wires, but each chip had its own data wire. When all those wires left the module, it yielded RAS, CAS, 12 address wires and 8 data wires, one from each memory chip.

Later, memory chips with 4 data wires became available. Then it was possible to build 30 pin SIMMs with just two memory chips, which you've probably seen before.

After 30 pin SIMMs came 72 pin SIMMs. A 72 pin SIMM still has 12 address wires. So how can they get up to 128MB of capacity? Well, they're wider for one thing. 32 bits wide. So 16M addresses X 32 bits = 16M addresses X 4 bytes = 64MB

(2^(12 X 2) X 4 = 64MB). Ooops. We're still short by a factor of two. It would appear that 64MB is the maximum size of a 72 pin SIMM. But we know from experience that it is not.

That is where banks come in. A 128MB SIMM is typically made from two banks of 64MB.

How is that done?

The 72 pin SIMM has four RAS wires. The computer has the ability to activate two of the RAS wires at a time.

So, a 128MB SIMM has all the chips that a 64MB SIMM has, and then it has them again. Two sets of chips as if there were two 64MB SIMMs on one board. The first set, or bank, of chips has all of its RAS pins connected to just two of the SIMM RASs. The second set/bank of chips is connected to the other two RAS wires.

When the computer wants bank 1, it uses the RAS 1 set of RAS wires. When the computer wants bank 2, it uses the RAS 2 set of RAS wires. If a chip's RAS line never gets used, it will ignore all the addresses and CAS signals and data that the computer is putting on the wires.

So, on a two bank SIMM, there are two sets of chips. The chips all share the same twelve address lines. Each chip in a bank shares its data wires with an identical chip in teh other bank. But each bank has its own set of RAS wires, and that's how the computer tells them apart.

Of course, this logic which allows distinguishing the RAS wires must be built into the computer.

Later 168 pin buffered DIMMs actually have a Bank(0) wire and I'm not exactly sure how that's used, but it's bound to be similar with differences caused by the buffering probably.

Now, why would a two bank SIMM work in one computer and not another computer, even though they both support two bank SIMMs (thepickles earlier question)?

Because there's more than one way to pair the RAS wires together. If there are RAS wires 1, 2, 3, and 4, and the logic board ties 1 & 3 together as a pair, and 2 & 4 as the second pair, but the SIMM connects 1 & 2 and 3 & 4, then they're wired incompatibly and all the RAS wires are always going to be active on any memory access, and the SIMM will appear as only half the capacity and probably not be very reliable because two chips (ones from each bank) are going to be trying to drive the same data at slightly different times.

I've seen this exact problem on the 6100. 128MB SIMMs which work in the Q605 didn't work in the PM6100 because the RAS lines are paired backwards.

Now, why do 64MB SIMMs work in the 6100 and not in the 7100/8100/9100? Simple, the 7100, 8100 and 9100 do not support 12 address lines on their SIMMs. They only support 11. So they support 11 + 11 = 22 bits of address => 4M addresses X 4bytes wide => 16MB per SIMM. However, they support two banks, so that's 16M X 2 banks => 32 MB. Yes, 32MB SIMMs are double banked 16MB SIMMs.

While the 6100, 7100, 8100 and 9100 all use exactly the same chipset (well slight difference in the 9100 AMIC) the latter three have an additional chip which decodes the address lines from the memory controller to support more SIMM sockets. So the higher address bits are sacrificed to provide support for more SIMMs. The 6100 runs its address lines straight to the SIMM sockets without the intervening logic and it is the only one which supports 12 bit addresses.

more thepickle questions:

======================

Is it technically possible to build a 72-pin SIMM with the following specs?

a) 2K refresh? faster than 2K refresh?

b) 64 or 128MB capacity? (I know this is possible, but bear with me here, please.)

c) more than two "banks?"

d) Any combination of the above three?

=======================

a) Yes, simple. The refresh simply refers to how many row addresses must be worked through during a refresh cycle. Eleven row addresses gives one 2K (2048) addresses. So only memory chips which have 11 address bits in their ROW are 2K. Memory chips which are 12 X have 4K row addresses and memory chips with 10 address bits have 1K (1024) row addresses.

Since the memory controller usually refreshes rows at a fixed pace, a memory chip with more row addresses needs to be able to tolerate a longer period between refreshes.

b) Yes, as you know

c) Possibly. I've never seen one, but there are four RAS lines. In theory, it should be possible to build a four bank 72 pin SIMM. The maximum memory per bank is still controlled by the address bits (12) and the width (4 bytes) so banks cannot have more than 64MB each.

d) If you have a 64MB or 128MB SIMM then you have 4K refresh because you have 12 row address bits. In theory, one could have a two bank 64MB SIMM built out of 11 X 12 (row X column) parts, but as far as I've seen, the row address is never shorter than teh column address, so I do not think anyone ever made 11 X 12 memory chips.

Finally, your 64MB two bank SIMM. That would have to be 12 X 11 X 2. That is 12 row bits X 11 column bits, by 2 banks. You would need a machine with a memory controller which is capable of addressing 12 X 11 chips. Most of them can't. They do 12 X 12 (if you're lucky) and 12 X 10 and 11 X 11, but 12 X 11 is rare. You might try it in the Q605/LC475.

-----------end of response --------------------

Part of the confusion I had was the from my loose definition of bank which I saw sometimes used interchangeably to refer to a memory stick. On top of that the correct term for what most people refer to a memory bank is actually supposed to be called memory rank now. I think this had a pretty thorough explanation:

https://www.digikey.ca/Site/Global/Layouts/DownloadPdf.ashx?pdfUrl=EE33DF78203D4692B71894E732852EA4

So for a 72-pin simm which is 32-bit, a rank would consist of a group of memory chips with the a total of 32 data lines.

Ok so now with all that clarified and with my current understanding are the following statements correct?

-Each memory rank is connected to a RAS line on the LC III memory controller.

-The LC III has 5 RAS lines.

-1 RAS line is connected to soldered memory rank on the logic board.

-2 RAS lines are connected to the existing memory socket (2 ranks).

-2 RAS lines are disconnected and could potentially be connected to another memory socket (2 ranks).

-Since there's only 11 address lines it's likely only 2K ram is supported by the memory controller of the LC III unless the 12th address line is also there but disconnected.

According to the developer doc for the LC III the memory map is defined for 36MB only. Seems to work for @max1zzz outside of that though.

The developer notes also shows A10 as not connected but that must be wrong or else you wouldn't be able to use 32MB simms.

I also found this interesting:

"At system startup, the boot code determines the amount of RAM installed in all banks and

then sets a RAM configuration register in Sonora."

Wonder what kind of configurations the Sonora chip supports. Couldn't find any dev notes on it though.

Attachments

Last edited:

I think these two pages were pretty good to give some insight into how SIMMs are wired and work:

https://www.cs.umd.edu/users/meesh/...s/ramguide/system/Web.htm#What is main memory

https://www.pjrc.com/tech/mp3/simm/datasheet.html

https://www.cs.umd.edu/users/meesh/...s/ramguide/system/Web.htm#What is main memory

https://www.pjrc.com/tech/mp3/simm/datasheet.html

I found a great webpage that I think answers all the questions I had regarding the wiring of 30-pin and 72-pin simms in a clear way:

https://www.retrotechnology.com/herbs_stuff/mac_banked_mem.txt

Heh, I wrote that posting at MacGurus. I was a moderator there a long time ago. I actually still had moderator privileges on their forums until they took them down.

There was so much excellent information in those forums....

Sigh.

I'm glad that posting was preserved at least. You gotta love Herb.

I also wrote a few tomes on the architecture of the X500 PCI Macs. That's probably gone forever.

Hey wait a second @trag! Are you the the same trag as the trag mentioned on that site?

"The thread started in 2001. "trag" who is/was a "Guru Moderator", responded on date 12-08-2010, 12:15 PM, as follows."

That would be quite to coincidence

Been using this handle since the 90s...

Well I'm glad it was preserved. It basically had all the information I was looking for with explanations unlike useless stuff like this from wikipedia:

It's like waaa..... how did you come up with 2 to the power of 27????

If you don't mind I think I'll make a copy of that memory information and post it on my website as another copy.

It's like waaa..... how did you come up with 2 to the power of 27????

If you don't mind I think I'll make a copy of that memory information and post it on my website as another copy.

If you don't mind I think I'll make a copy of that memory information and post it on my website as another copy.

It's more than okay with me. I'm glad to see it preserved. MacGurus might have a copyright depending on the terms of their forums, but I doubt they'll notice and they probably wouldn't mind anyway.

Thanks for jumping in with both feet, bud! I know work has you well and truly knackered.I don't really have time to sort out the whole diagram, but hopefully clarification/confirmation will be in the following details.

One review question: I have a suspicion that we figured that addressing two 32MB 72pin SIMMs from a bank of four 30pin SIMMs was the way to go for converting something like the SE/30 or IIsi over to 72pin SIMMs? 64MB SIMMs was not the way to go? Do you remember offhand? So, so long ago, sigh!

edit: curious about how that jibes with setup of extra SIMMs in LCIII and Q605, not off topic exactly. Seems like all one big can-o-worms to me.

Last edited: